TMS320C6674ACYPA Multicore Fix/Float Pt Dig Sig Proc

♠ Produktbeschreibung

| Produkteigenschaften | Attributwert |

| Hersteller: | Texas Instruments |

| Produktkategorie: | Digitale Signalprozessoren und Controller – DSP, DSC |

| Produkt: | DSPs |

| Serie: | TMS320C6674 |

| Montageart: | SMD/SMT |

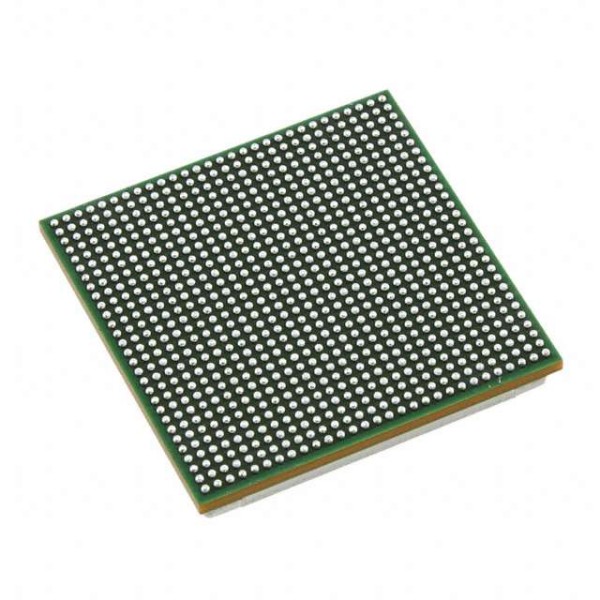

| Verpackung / Koffer: | FCBGA-841 |

| Kern: | C66x |

| Anzahl der Kerne: | 4 Kerne |

| Maximale Taktfrequenz: | 1 GHz, 1,25 GHz |

| L1-Cache-Befehlsspeicher: | 4 x 32 kB |

| L1-Cache-Datenspeicher: | 4 x 32 kB |

| Programmspeichergröße: | - |

| Daten-RAM-Größe: | - |

| Betriebsspannung: | 900 mV bis 1,1 V |

| Minimale Betriebstemperatur: | - 40 °C |

| Maximale Betriebstemperatur: | + 100 °C |

| Verpackung: | Tablett |

| Marke: | Texas Instruments |

| Datenbusbreite: | 8 Bit/16 Bit/32 Bit |

| Anweisungstyp: | Festkomma/Gleitkomma |

| MMACS: | 160000 MMACS |

| Feuchtigkeitsempfindlich: | Ja |

| Anzahl der E/As: | 16 E/A |

| Anzahl der Timer/Zähler: | 12 Zeitschaltuhr |

| Produkttyp: | DSP – Digitale Signalprozessoren und Controller |

| Fabrikpackungsmenge: | 44 |

| Unterkategorie: | Eingebettete Prozessoren und Controller |

| Versorgungsspannung - Max: | 1,1 V |

| Versorgungsspannung - Min: | 900 mV |

| Stückgewicht: | 0,173396 Unzen |

♠ Multicore-Fest- und Gleitkomma-Digitalsignalprozessor

Der TMS320C6674 DSP ist ein leistungsstarker Fest-/Gleitkomma-DSP, der auf der KeyStone-Multicore-Architektur von TI basiert. Dank des neuen und innovativen C66x DSP-Kerns erreicht dieser Baustein eine Taktfrequenz von bis zu 1,25 GHz. Für Entwickler einer breiten Palette von Anwendungen, wie beispielsweise unternehmenskritische Systeme, medizinische Bildgebung, Test und Automatisierung sowie weitere Anwendungen mit hohen Leistungsanforderungen, bietet der TMS320C6674 DSP von TI eine kumulative DSP-Frequenz von 5 GHz und ermöglicht eine energieeffiziente und benutzerfreundliche Plattform. Darüber hinaus ist er vollständig abwärtskompatibel mit allen bestehenden Fest- und Gleitkomma-DSPs der C6000-Familie.

Die KeyStone-Architektur von TI bietet eine programmierbare Plattform mit verschiedenen Subsystemen (C66x-Kerne, Speichersubsystem, Peripheriegeräte und Beschleuniger). Sie nutzt innovative Komponenten und Techniken, um die Kommunikation innerhalb und zwischen Geräten zu optimieren und so den effizienten und reibungslosen Betrieb der verschiedenen DSP-Ressourcen zu gewährleisten. Zentrale Komponenten dieser Architektur sind der Multicore Navigator, der ein effizientes Datenmanagement zwischen den verschiedenen Gerätekomponenten ermöglicht. TeraNet ist eine blockierungsfreie Switch Fabric, die einen schnellen und konkurrenzfreien internen Datenverkehr ermöglicht. Der Multicore Shared Memory Controller ermöglicht den direkten Zugriff auf gemeinsam genutzten und externen Speicher, ohne die Switch Fabric-Kapazität zu beanspruchen.

• Vier TMS320C66x™ DSP Core Subsysteme (C66x CorePacs), jedes mit

– 1,0 GHz oder 1,25 GHz C66x Fest-/Gleitkomma-CPU-Kern

› 40 GMAC/Core für Festkomma @ 1,25 GHz

› 20 GFLOP/Core für Gleitkommazahlen bei 1,25 GHz

- Erinnerung

› 32 KB L1P pro Kern

› 32 KB L1D pro Kern

› 512 KB lokales L2 pro Kern

• Multicore Shared Memory Controller (MSMC)

– 4096 KB MSM SRAM-Speicher, gemeinsam genutzt von vier DSP C66x CorePacs

– Speicherschutzeinheit für MSM SRAM und DDR3_EMIF

• Multicore-Navigator

– 8192 Mehrzweck-Hardware-Warteschlangen mit Warteschlangenmanager

– Paketbasiertes DMA für Zero-Overhead-Übertragungen

• Netzwerk-Coprozessor

– Packet Accelerator ermöglicht die Unterstützung von

› Transportebene IPsec, GTP-U, SCTP, PDCP

› L2-Benutzerebene PDCP (RoHC, Luftverschlüsselung)

› 1-Gbit/s-Wire-Speed-Durchsatz bei 1,5 MPaketen pro Sekunde

– Security Accelerator Engine ermöglicht Unterstützung für

› IPSec, SRTP, 3GPP, WiMAX Air Interface und SSL/TLS-Sicherheit

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (256-Bit-Hash), MD5

› Bis zu 2,8 Gbit/s Verschlüsselungsgeschwindigkeit

• Peripheriegeräte

– Vier Lanes von SRIO 2.1

› 1,24/2,5/3,125/5 GBaud-Betrieb pro Lane unterstützt

› Unterstützt direkte E/A und Nachrichtenübermittlung

› Unterstützt vier 1×-, zwei 2×-, eine 4×- und zwei 1×- + eine 2×-Link-Konfigurationen

– PCIe Gen2

› Einzelner Port unterstützt 1 oder 2 Spuren

› Unterstützt bis zu 5 GBaud pro Lane

– Hyperlink

› Unterstützt Verbindungen zu anderen Geräten mit KeyStone-Architektur und bietet so Ressourcenskalierbarkeit

› Unterstützt bis zu 50 Gbaud

– Gigabit Ethernet (GbE) Switch-Subsystem

› Zwei SGMII-Ports

› Unterstützt 10/100/1000 Mbit/s-Betrieb

– 64-Bit DDR3-Schnittstelle (DDR3-1600)

› 8 GB adressierbarer Speicherplatz

– 16-Bit EMIF

– Zwei Telecom Serial Ports (TSIP)

› Unterstützt 1024 DS0s pro TSIP

› Unterstützt 2/4/8 Lanes mit 32,768/16,384/8,192 Mbit/s pro Lane

– UART-Schnittstelle

– I²C-Schnittstelle

– 16 GPIO-Pins

– SPI-Schnittstelle

– Semaphormodul

– Zwölf 64-Bit-Timer

– Drei On-Chip-PLLs

• Handelstemperatur:

– 0 °C bis 85 °C

• Erweiterte Temperatur:

– -40°C bis 100°C

• Missionskritische Systeme

• Hochleistungs-Computersysteme

• Kommunikation

• Audio

• Video-Infrastruktur

• Bildgebung

• Analytik

• Vernetzung

• Medienverarbeitung

• Industrielle Automatisierung

• Automatisierung und Prozesssteuerung