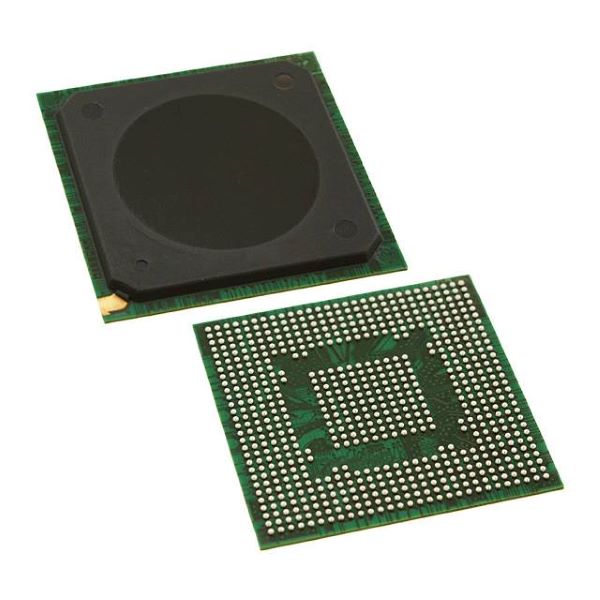

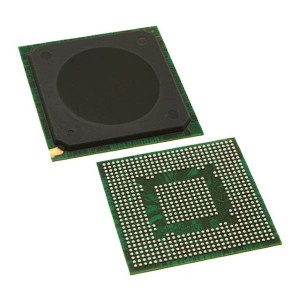

P1020NXN2HFB Mikroprozessoren – MPU 800/400/667 ET NE r1.1

♠ Produktbeschreibung

| Produkteigenschaften | Attributwert |

| Hersteller: | NXP |

| Produktkategorie: | Mikroprozessoren - MPU |

| RoHS: | Details |

| Montageart: | SMD/SMT |

| Verpackung/Koffer: | TEPBGA-689 |

| Serie: | P1020 |

| Kern: | e500 |

| Anzahl der Kerne: | 2 Kerne |

| Datenbusbreite: | 32 Bit |

| Maximale Taktfrequenz: | 800 MHz |

| L1-Cache-Befehlsspeicher: | 2 x 32 kB |

| L1-Cache-Datenspeicher: | 2 x 32 kB |

| Betriebsspannung: | 1 V |

| Minimale Betriebstemperatur: | - 40 °C |

| Maximale Betriebstemperatur: | + 125 °C |

| Verpackung: | Tablett |

| Marke: | NXP Semiconductors |

| E/A-Spannung: | 1,5 V, 1,8 V, 2,5 V, 3,3 V |

| Anweisungstyp: | Gleitkomma |

| Schnittstellentyp: | Ethernet, I2C, PCIe, SPI, UART, USB |

| L2 Cache Befehls-/Datenspeicher: | 256 kB |

| Speichertyp: | L1/L2-Cache |

| Feuchtigkeitsempfindlich: | Ja |

| Anzahl der E/As: | 16 E/A |

| Prozessorserie: | QorIQ |

| Produkttyp: | Mikroprozessoren - MPU |

| Fabrikpackungsmenge: | 27 |

| Unterkategorie: | Mikroprozessoren - MPU |

| Handelsname: | QorIQ |

| Watchdog-Timer: | Kein Watchdog-Timer |

| Teile-Aliase: | 935310441557 |

| Stückgewicht: | 5,247 g |

• Zwei leistungsstarke 32-Bit-Kerne, basierend auf der Power Architecture®-Technologie:

– 36-Bit physikalische Adressierung

– Unterstützung für Gleitkommazahlen mit doppelter Genauigkeit

– 32 KByte L1-Befehlscache und 32 KByte L1-Datencache für jeden Kern

– 533 MHz bis 800 MHz Taktfrequenz

• 256 KByte L2-Cache mit ECC. Auch als SRAM und Stashing-Speicher konfigurierbar.

• Drei 10/100/1000 Mbit/s erweiterte Drei-Geschwindigkeits-Ethernet-Controller (eTSECs)

– TCP/IP-Beschleunigung, Dienstgüte und Klassifizierungsfunktionen

– IEEE® 1588-Unterstützung

– Verlustfreie Flusskontrolle

– MII, RMII, RGMII, SGMII

• Hochgeschwindigkeitsschnittstellen, die verschiedene Multiplexing-Optionen unterstützen:

– Vier SerDes mit bis zu 2,5 GHz/Lane, gemultiplext über Controller

– Zwei PCI-Express-Schnittstellen

– Zwei SGMII-Schnittstellen

• High-Speed-USB-Controller (USB 2.0)

– Host- und Geräteunterstützung

– Verbesserte Host-Controller-Schnittstelle (EHCI)

– ULPI-Schnittstelle zu PHY

• Verbesserter sicherer digitaler Hostcontroller (SD/MMC)

• Erweiterte serielle Peripherieschnittstelle (eSPI)

• Integrierte Sicherheits-Engine

– Protokollunterstützung umfasst ARC4, 3DES, AES, RSA/ECC, RNG, Single-Pass-SSL/TLS

– XOR-Beschleunigung

• 32-Bit DDR2/DDR3 SDRAM-Speichercontroller mit ECC-Unterstützung

• Programmierbarer Interrupt-Controller (PIC) kompatibel mit dem OpenPIC-Standard

• Ein Vierkanal-DMA-Controller

• Zwei I2 C-Controller, DUART, Timer

• Verbesserter lokaler Buscontroller (eLBC)

• TDM

• 16 allgemeine E/A-Signale

• Betriebsübergangstemperaturbereich (Tj): 0–125 °C und –40 °C bis 125 °C (Industriespezifikation)

• 31 × 31 mm 689-poliges WB-TePBGA II (temperaturgesteigertes Kunststoff-BGA mit Drahtbond)